- 您现在的位置:买卖IC网 > Sheet目录1250 > TURBO-DECO-XM-UT3 (Lattice Semiconductor Corporation)SITE LICENSE TURBO DECODER XP

�� �

�

Lattice� Semiconductor�

�Turbo� Decoder� User’s� Guide�

�3GPP2�

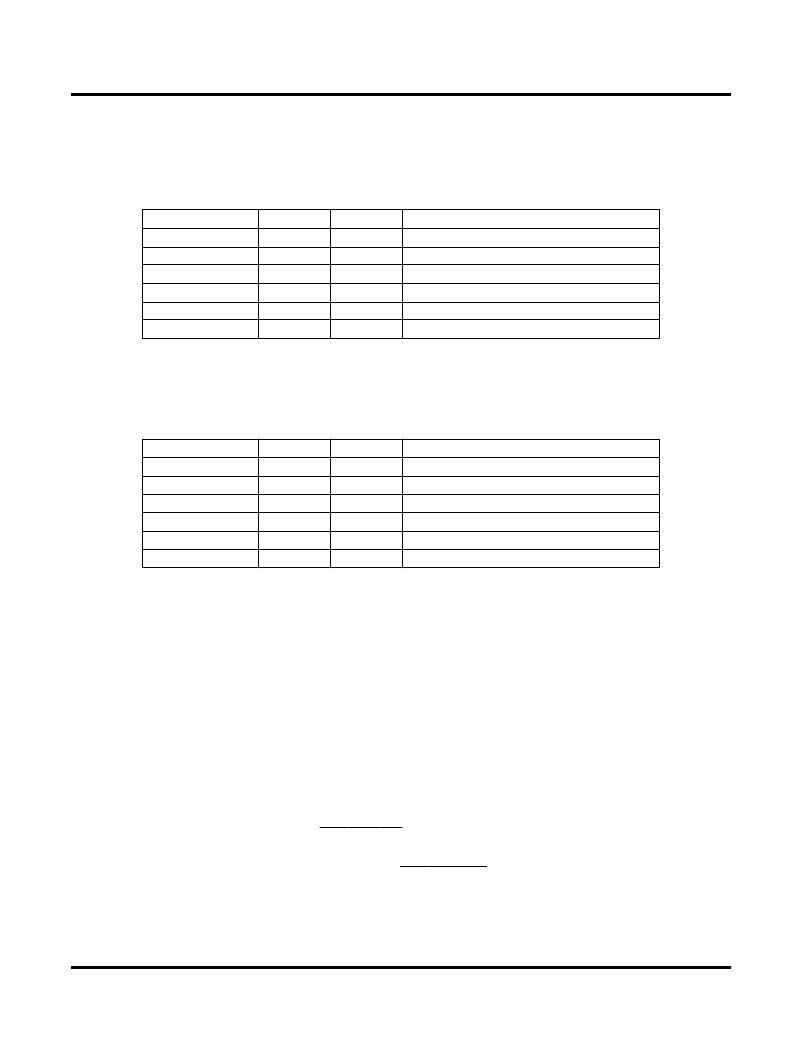

�For� the� 3GPP2� decoder� type,� in� the� case� that� an� external� memory� is� selected;� the� following� additional� pins� are�

�required.� It� is� assumed� that� data� and� parity� are� stored� in� different� memory� buffers.� Non-interleaved� and� interleaved�

�parity� are� stored� in� different� buffers.�

�Table� 7.� Additional� I/Os� Due� to� External� Memory� for� 3GPP2�

�Port� Name�

�g1_par2_odd1�

�g2_par2_odd1�

�g1_par2_even1�

�g2_par2_even1�

�wren_par3_buf1�

�wren_par4_buf1�

�I/O� Type�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Width�

�3-6�

�3-6�

�3-6�

�3-6�

�1�

�1�

�Signal� Description�

�Parity� 3� (systematic)� data� port� 1�

�Parity� 3� (systematic)� data� port� 2�

�Parity� 4� (interleaved)� data� port� 1�

�Parity� 4� (interleaved)� data� port� 2�

�Write� enable� for� parity� 3� (systematic)�

�Write� enable� for� parity� 4� (interleaved)�

��In� the� case� where� a� double� buffer� is� selected� along� with� the� external� memory,� the� I/O� pins� in� Table� 8� will� also� be�

�added� to� the� core� for� exchanging� data� with� the� second� buffer� in� the� case� of� 3GPP2.�

�Table� 8.� Additional� I/Os� Due� to� Double� Buffering� for� 3GPP2�

�Port� Name�

�g1_par2_odd2�

�g2_par2_odd2�

�g1_par2_even2�

�g2_par2_even2�

�wren_par3_buf2�

�wren_par4_buf2�

�I/O� Type�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Width�

�3-6�

�3-6�

�3-6�

�3-6�

�1�

�1�

�Signal� Description�

�Parity� 3� (systematic)� data� port� 1�

�Parity� 3� (systematic)� data� port� 2�

�Parity� 4� (interleaved)� data� port� 1�

�Parity� 4� (interleaved)� data� port� 2�

�Write� enable� for� parity� 3� (systematic)�

�Write� enable� for� parity� 4� (interleaved)�

��IPexpress?� User-Con?gurable� Core�

�The� Turbo� Decoder� core� is� an� IPexpress� User-Con?gurable� IP� core,� which� allows� designers� to� con?gure� the� IP� and�

�generate� netlists� as� well� as� simulation� ?les� for� use� in� designs.� The� IPexpress� ?ow� also� supports� a� hardware� evalu-�

�ation� capability,� making� it� possible� to� create� versions� of� the� IP� core� that� operate� in� hardware� for� a� limited� period� of�

�time� without� requiring� the� purchase� of� an� IP� license.�

�To� download� a� full� evaluation� version� of� this� IP� core,� please� go� to� the� Lattice� IP� Server� tab� in� the� ispLEVER� ?� IPex-�

�press� GUI� window.� All� ispLeverCORE?� IP� cores� available� for� download� are� visible� on� this� tab.�

�References�

�The� Lattice� Turbo� Decoder� IP� core� is� compliant� with� two� standards:� 3GPP� and� CCSDS.� More� information� about�

�each� standard� can� be� referenced� at� the� following� locations.�

�?� The� 3rd� Generation� Partnership� Project� (www.3gpp.org)� provides� speci?cations� to� 3GPP� TS� 25.212� v4.2.0�

�(2001-09)� standards.�

�?� The� Consultative� Committee� for� Space� Data� Systems� (www.ccsds.org)� provides� speci?cations� to� CCSDS� 101.0-�

�B-5� standards.�

�13�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TVB058SA-L

SURGE PROTECTOR 58V DO-214AA

TVB200SA-L

SURGE PROTECTOR 200V BREAKOVER

TVB200SC-L

SURGE PROTECTOR 200V BREAKOVER

TVB270SB-L

SURGE PROTECTOR 270V DO-214AA

TVB270SC-L

SURGE PROTECTOR 270V DO-214AA

TVB300SA-L

SURGE PROTECTOR 300V DO-214AA

TVB300SB-L

SURGE PROTECTOR 300V DO-214AA

TVB300SC-L

SURGE PROTECTOR 300V DO-214AA

相关代理商/技术参数

TURBO-DECO-XP-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-E2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-O4-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-P2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-PM-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-SC-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-X2-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-X2-UT3

功能描述:开发软件 TURBO ENCODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors